Intel’s New Programmable Chips Next Year to Replace Aging Products

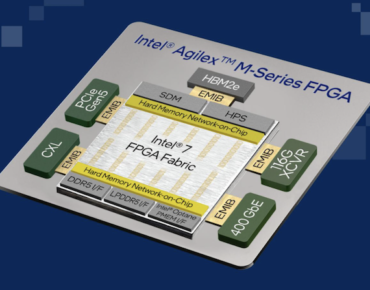

Intel today introduced product details for the Intel Agilex M-Series FPGAs, built on Intel 7 process technology, the industry’s highest memory bandwidth FPGAs with in-package HBM DRAM. Credit: Intel Corporation

Intel shared its latest roadmap of programmable chips, and doesn’t want to dig itself into a hole by following AMD’s strategy in the area.

“We’re thankfully not matching their strategy,” said Shannon Poulin, corporate vice president for the datacenter and AI group at Intel, in response to a question posed by HPCwire during a press briefing.

The updated roadmap pieces together Intel’s strategy for FPGAs, or field programmable gate arrays, in line with its manufacturing advances.

FPGAs can be programmed to carry out a range of functions as AI chips and network acceleration. Companies also use FPGAs to test chip designs or prototype applications.

Intel’s been on a holding pattern on FPGAs, releasing the last major Agilex chip in 2021, which was made on the 10nm SuperFin process.

The next major Agilex product – which is more a manufacturing upgrade – will be released in 2023-2024. The M-series FPGA will be on an upgraded 10nm process, which Intel calls “Intel 7.”

The followup, the next-generation Agilex chip based on a new architecture, will also come in the 2023-2024 timeframe on Intel 7.

Poulin, who took over the FPGA division last year, acknowledged that the company hasn’t kept pace in meeting suppliers’ needs. Intel had neither availability or a portfolio of FPGAs for the low-end market on a modern manufacturing process, Poulin said.

“I really felt like we needed to look at the supply chain. We had many of our products – we still have many of our products – on legacy supply nodes, many of those nodes not made at Intel, and I’m talking about nodes that are, you know, 5-10-20 years old, in some cases,” Poulin said.

Manufacturing consulting firm Jabil, which integrates chips into projects for industrial clients, has said it expects FPGA shortages to go into 2023.

There’s a big demand for FPGAs in modern equipment in 5G and robotics where cutting edge FPGAs, made on modern processes, is becoming really important, Poulin said.

“We’re moving our whole portfolio over to Intel manufacturing,” he said.

Intel’s making a range of advances in its manufacturing processes, including the use of “chiplet” technology that can package together a range of chips in a single die. Intel is designing an FPGA for that, which brings in PCIe 5.0 and the CXL interconnect, and can be paired with a range of chips, such as AI accelerators, GPUs, or x86 and RISC-V CPUs in one integrated chip. Intel has been sampling that product and will bring them to production soon, Poulin said.

The company is working with partners like Texas Instruments, which mostly makes analog chips, to connect the FPGA to third-party chiplets. That is done via an interface Intel calls AIB (Advanced Interface Bus).

“We’re moving to more chiplet architecture and more modular capability which really opens up a number of opportunities not just for PSG … but also for the broader company,” Poulin said.

Also on the roadmap is Agilex D-series, which is for the mid-range market. The chip will have 100,000 logic elements, low-power DDR5 memory, and a new type of “smart fabric” that will provide a performance boost. The initial chips will sample in 2023, with volume shipments starting in 2024. The FPGA is targeted at industrial, communications, robotics and other markets.

The next Agilex chip codenamed Sundance Mesa will be about half the size of the D-series chip with about 50,000 logic elements. It will be for artificial intelligence and consumer-oriented applications. Intel hasn’t assigned a series name to this chip.

Intel has been doing chiplets with its Stratix and Agilex FPGAs for four years, but will evolve it to support new interfaces like UCIe, which is emerging as the interconnect to link up diverse cores inside a single chip package.

Intel to an extent is relying on chiplets and associated interfaces like UCIe and CXL, to move its FPGA strategy forward. That relies heavily on the company’s manufacturing strategy, which isn’t moving forward as planned with delays in shipments for chips such as Xeon processors codenamed Sapphire Rapids and the Gaudi 2 AI chip.

In the meanwhile, AMD has moved ahead with quick integration of Xilinx, which it acquired earlier this year after a long review period. AMD wasted no time releasing a cohesive roadmap that included CPUs, GPUs, software-defined FPGAs and fixed-function ASICs.

AMD executives are making the rounds of chip conferences talking about the FPGA and ASIC roadmap. FPGAs can carry out chip functions using software, but AMD is pairing fixed function logic, like ASICs, to programmable logic adapters like FPGAs where one can layer in customizations such as custom header extensions, or add or remove new accelerator functions on the programmable logic.

Intel is playing catch up, but Poulin said the company wants to get its strategy right even if it takes time. The modular approach – which will be made possible by interfaces like UCIe and CXL – will allow Intel to create a more flexible chip design, Poulin said.

“I think it’s fair … that we’re still filling out our portfolio, but we are not going to follow them strategy wise down that rabbit hole of hardening IP that people don’t want or most people don’t want,” Poulin said.

Poulin said there are two choices where one could choose to harden IP – on the fabric itself, or on a chiplet, which Intel has with the AIB interface.

“One of the things you don’t want to do, which is one of the things [AMD’s] Versal has done, is hardened a bunch of things that a subset of the people will use and not have a modular way of actually making exactly the right product that somebody wants, because then you end up cost (infrastructure wise), leakage (current wise), and with a product that is over designed for an individual market,” Poulin said.

Intel’s strategy is playing out well in the infrastructure processing unit (IPU) space, where the company has hardened IP on the fabric.

“We’re going to have a modular approach so that we can put exactly the hard IP on exactly the customers that want it,” Poulin said.

But Intel has its challenges going forward, which partly relies on the company meeting its manufacturing roadmap. Intel CEO Pat Gelsinger in 2021 set an aggressive roadmap of advancing four nodes in five years, which is much quicker than the typical two-year advance in chip manufacturing. Another big question for Intel remains whether the company will be able to personalize those chips, which the company mainly does for top customers with large orders of custom chips.