Intel Says UCIe to Outpace PCIe in Speed Race

Intel has shared more details on a new interconnect that is the foundation of the company’s long-term plan for x86, Arm and RISC-V architectures to co-exist in a single chip package.

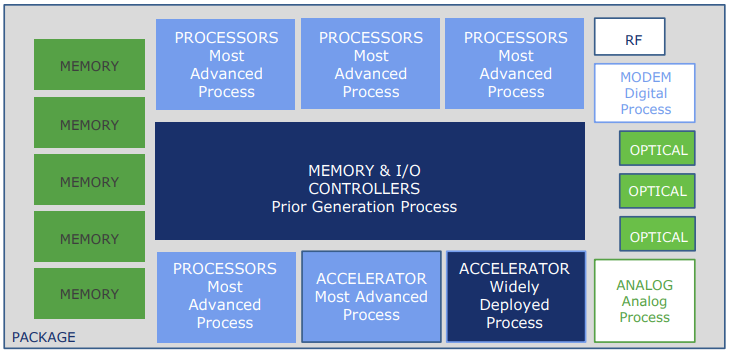

The semiconductor company is taking a modular approach to chip design with the option for customers to cram computing blocks such as CPUs, GPUs and AI accelerators inside a single chip package. Intel with nine other companies in March established the Universal Chiplet Interconnect Express standard as a high-bandwith, low-latency connector for those computing blocks to communicate inside a chip.

“The first incarnation of UCIe will be about 12 gigabits per second per pin, and there’ll be another one that is about 16 gigabits per second,” said Bob Brennan, vice president and general manager for customer solution engineering of Intel Foundry Services on Tuesday while speaking at a breakout session at Intel’s Vision conference being held this week in Grapevine, Texas.

“If you look at the bandwidth over power, [UCIe] is far superior to something like PCI Express,” Brennan said.

The first incarnation of UCIe will be roughly four times faster than PCI-Express over the same distance with a limited number of pipes, Brennan said. UCIe has the potential to be well over 10 to 20 times faster than PCI Express with more pipes between channels, Brennan said.

The comparisons were relative to distance. UCIe is designed for a very short distance on a substrate at the chip level, while PCI Express is implemented at the motherboard level, in which data is transferred over a longer distance and electrical requirements are different, Brennan said.

“Think of UCIe being the PCIe but for chips,” Brennan said.

The UCIe founding members included AMD, Arm, Taiwan Semiconductor Manufacturing Co., Microsoft, Qualcomm and Samsung. Nvidia later that month announced it would support the UCIe standard, though its name still isn’t listed on UCIe’s website.

Apple, which designs most of its hardware internally, is not a member of UCIe

SOC package level construction. Mix and match dies from multiple sources with different packaging options. Source: UCIe Consortium

“It’s a first incarnation of UCIe, we built this with a broad consortium of partners and our competitors to put this into the market. I was very pleased to see that come together very quickly,” Brennan said. He did not provide a timeline on when the specification would be released.

Intel is opening up its chips so its homegrown x86 cores can be packaged alongside computing cores based on Arm or RISC-V architecture. For example, a Xeon chip could co-exist with a RISC-V or Arm AI accelerator in a package. Brennan called the package of cores a “chiplet chassis,” with computing blocks connected via UCIe channels.

“The concept of a chiplet chassis is that we would provide a silicon chassis that would be a reference design for our customers to work with, similar conceptually to how we do a board design. Instead, this is chip design,” Brennan said.

UCIe will support packaging options such as Intel’s EMIB (Embedded Multi-Die Interconnect Bridge) and TSMC’s CoWoS (Chip-on-Wafer-on-Substrate) technologies.

“In the future we have to take care of the protocol layer,” Brennan said.

There’s support initially for the CXL (Compute Express Link) protocol, an industry standard built on PCIe 5.0 to connect the CPU chip package to accelerators, storage and memory components. Many other protocols could be supported in the future, including CHI (Coherent Hub Interface), which is part of ARM-backed AMBA (Advanced Microcontroller Bus Architecture). The goal is to add the ability to also map out to proprietary protocols, and also backward compatibility on protocols so companies can protect their investments in software.

“We also plan to spec out in the future with our partners in the consortium different form factors, management, security and many, many things,” Brennan said.

Brennan shared several examples of on-chip UCIe design. One was a chip package with a CPU subsystem connecting with hardware accelerators and management and security blocks via UCIe, with EMIB packaging used to connect to chip to disaggregated DDR5 memory and PCIe links.

Related

With over a decade’s experience covering the HPC space, Tiffany Trader is one of the preeminent voices reporting on advanced scale computing today.