Oracle Unfolds Sparc Roadmap, Fujitsu Boosts Sparc64 X Clocks

With Intel having refreshed its Xeon E5 and E7 chips recently and IBM getting ready to debut its Power8 chips at the end of the month, Sparc partners Oracle and Fujitsu have to make a little noise to keep people thinking about their chips and platforms.

To that end, Oracle has updated its roadmap for its Sparc T and M series of processors for its own line of systems, and Fujitsu has announced that it has been able to sort through the bins of Sparc64-X+ processors used in its M10 systems and find some variants that run at significantly higher clock speeds than the first batch of chips that came out last summer when they were previewed.

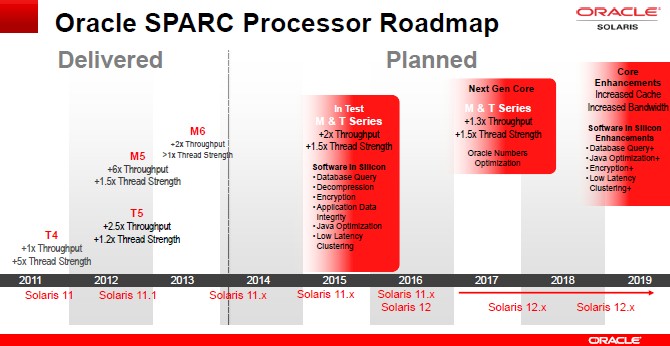

Oracle did not provide any commentary on its roadmap update, and as is usually the case, it did not respond to a request for an interview to clarify some of the items on the roadmap. If the past is any indication of the future, then Oracle will be a lot more forthcoming about what its plans are at the OpenWorld event it hosts at the end of September this year. Under normal circumstances, Oracle would be making a chip announcement around that time, and as you can see from the roadmap below, that doesn't look like it is in the cards in 2014:

There is a whole lot of gray space up there in 2014, which means no new processors are coming out from Oracle this year. As Fujitsu has done, it is possible that Oracle could work with its fab partner, Taiwan Semiconductor Manufacturing Corp, to sort through the bins and find Sparc T5 and M6 processors that run at higher clock speeds.

The Sparc T and M chips are both based on Oracle's "S3" core and they have varying amounts of cores, cache memories, and NUMA scalability to meet the needs of different kinds of workloads in the datacenter. The T chips generally have more cores and less L3 cache memory than the M chips. The current Sparc T5 has sixteen cores and 128 threads with 8 MB of L3 cache on the die and the ability to address up to 512 GB of memory per socket; the on-chip NUMA electronics allow the T5 to be used in machines with one, two, four, or eight sockets. The M5 chip has six of the S3 cores, each with eight threads, and 48 MB of L3 cache; it can address up to 1 TB of memory per socket. The M6 kicker that came pretty fast on its heels doubled the cores to 12 and the threads to 96 while holding the L3 cache steady at 48 MB. The M5 scaled up to 32 sockets with the "Bixby" interconnect, while the M6 can, in theory, scale up to 96 sockets with Bixby.

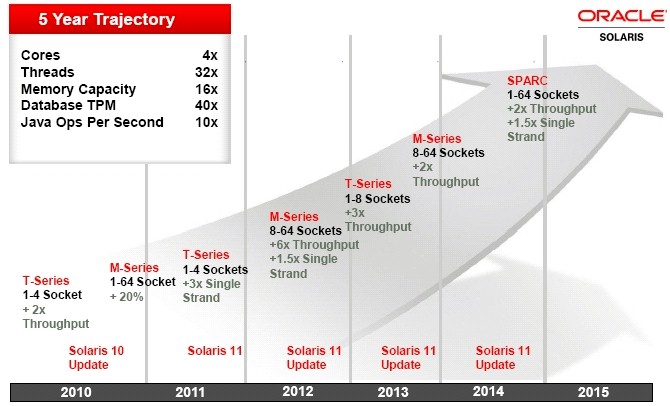

Oracle's long-term goal, stated at the end of 2009 and reiterated in 2010 in the roadmap below, was to create machines that would have four times as many cores, 32 times as many cores, and 16 times as much memory as then-current Sparc-based systems.

This roadmap's timing was a bit vague, but it looked like the goal was to reach a machine that scaled from 1 to 64 sockets with those capabilities by the end of 2014 or early 2015. That is clearly not the plan, and that is no surprise given the fact that creating Sparc processors and massive NUMA systems that scan scale as far as Oracle wants to go is a tough bit of engineering. And Oracle does not have a server business with enough revenues and profits, much less shipments, to do a major update of processors every year. It could use the tock-tock model Intel employs, and that is why we say there is a chance that Oracle could get faster T5 and M6 processors into the field in late 2014 or early 2015.

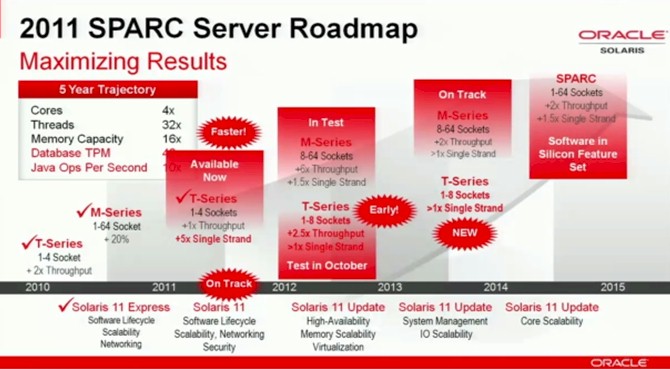

The Sparc roadmap from 2011 clearly shows that Oracle was planning to get the M6 processors in the field in early 2014, and in fact it pulled these in early and got them out the door in September last year in the M6-32 systems. In early 2012, Oracle pulled the Sparc T5 chips into late 2012, and then changed its mind and pushed them back out into early 2013 where they originally were supposed to come to market.

Having chip roadmaps move around is perfectly normal, and as EnterpriseTech has pointed out in the past, a microprocessor that comes out perfectly on time is the exception, not the rule. The chips are increasingly complex, and the processes that are used to make them are also getting more byzantine and really, the amazing thing is that we get chips that come out along the lines of Moore's Law at all. It is amazing what money and concentration can do.

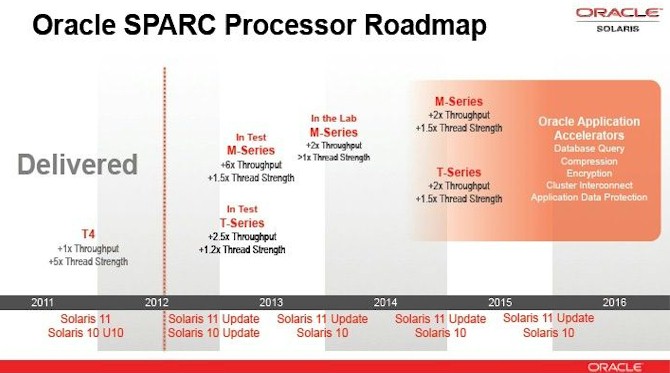

The Sparc roadmap from 2012, seen below, showed customers to expect an update to both processors possibly late in 2014 but, assuming the center of gravity of the words is the most likely date, perhaps early in 2015. These T6 and M7 processors would have clock speeds around 1.5X higher than their T5 and M6 predecessors and the resulting systems would offer 2X higher overall system throughput on the database and middleware workloads that Oracle judges itself by. The company said nothing about the future of the Sparc product line beyond this point.

This did clarify that there would be both T and M series chips and systems to use them; up until this point, it looked as if Oracle was going to try to converge to one processor. This converged Sparc processor is now removed from the 2014 roadmap at the top of this story, and now you can see that Oracle now plans a kicker using the current S3 cores in 2015 with circuits specifically designed to speed up database queries, data decompression, encryption, and Java. This 2015 edition of the Sparc – presumably to be called the Sparc T6 and the Sparc M7 – will also include low latency clustering that is an upgrade to the current "Bixby" interconnect, which is absolutely no slouch at all and which allows Oracle to build a machine with 96 sockets and 96 TB of main memory. (At the moment, Oracle is topping Bixby out at 32 sockets and 32 TB with the Sparc M6-32 system.)

The Sparc T5 processors ran at 3.6 GHz and had sixteen cores with eight threads per core. The latest roadmap implies that Oracle will be able to use a process shrink, presumably to TSMC's 20 nanometer processes from the 28 nanometer etching used with the T5, M5, and M6, to boost the clock speed. TSMC says that this shift to 20 nanometers at its fabs can yield 30 percent higher clock speeds, give 1.9 times the circuit density, or consume 25 percent less power than chips using the 28 nanometer processes. To get "thread strength" up by a factor of 1.5X, Oracle has to use most of this shrink for clock speed enhancements with some left over to add more threads to each core and maybe more cores to each die. It all depends on how large Oracle wants the chips to get and if it needs to maintain socket compatibility. Pushing the clock speed on the future Sparc T6 to 4.5 GHz gets the chip half-way there on the thread boost, and adding more L3 cache memory for the 16 cores could push it the rest of the way without substantially changing the S3 cores on the die. To double the throughput, Oracle could simply move to twelve threads per core or, less likely, move to 32 cores per die. Suffice it to say, Oracle has options to get there.

Ditto for the M7 chip expected at the same time in 2015 or, if you read the chart carefully, perhaps in early 2016. The idea is to get 1.5X more performance per thread and 2X the throughput compared to the Sparc M6 chip – and to do so while sticking with the S3 core.

In 2017, Oracle will put out a new core, presumably to be called an S4. The per-thread performance will be boosted by 50 percent again, and the system throughput by 30 percent, for both the T and M variants of the chips. If Oracle doesn't lockstep its naming conventions, these chips will be called the T7 and M8, and will have a feature called "Oracle Numbers Optimization," presumably something that affects Wall Street's view of the company's quarterly financials. . . . Beyond that, in 2019, there are core enhancements adding more cache and more bandwidth to the S4 cores as well as enhancements to the software acceleration features for database queries, Java, and encryption as well as tweaks to the low-latency NUMA clustering.

Oracle did not say how far it would push scalability on either the T or M machines, but it could scale up the boxes or just work to lower the latencies to make the NUMA clustering tighter and more efficient.

On the software front, we can look for Solaris 12 to come out in 2016, and for Solaris 11, which came out in November 2011, to continue to get updates about once a year between then and now. It was about seven years between Solaris 10 and Solaris 11, so the space between the releases is tightening up a bit. Then again, the features are generally not as dramatic with each successive release, too, so that stands to reason. There is always plenty of work to be done down in the kernel, hypervisor, and network stack, of course.

In a separate but related announcement, inasmuch as Oracle resells Fujitsu's M10 servers, based on the Japanese company's Sparc64-X processor, Fujitsu has delivered a "plus" variant of its sixteen-core chip that now runs at 3.7 GHz instead of the 3.5 GHz target speed. THese are both significantly faster than the 2.8 GHz speed of the Sparc64-X chip. This sixteen-core chip, which includes a number of microarchitecture enhancements, is used in the single-socket M10-1, the four-socket M10-4M, and the 64-socket M10-4S, all of which run Solaris 10 and 11. It is not clear at press time what premium Oracle and Fujitsu are charging for the 30 percent boost in clock speed for the new Sparc64-X+ chips.